- 您现在的位置:买卖IC网 > Sheet目录3841 > PIC16F737-I/SP (Microchip Technology)IC PIC MCU FLASH 4KX14 28DIP

2009 Microchip Technology Inc.

DS39636D-page 221

PIC18F2X1X/4X1X

18.6

A/D Conversions

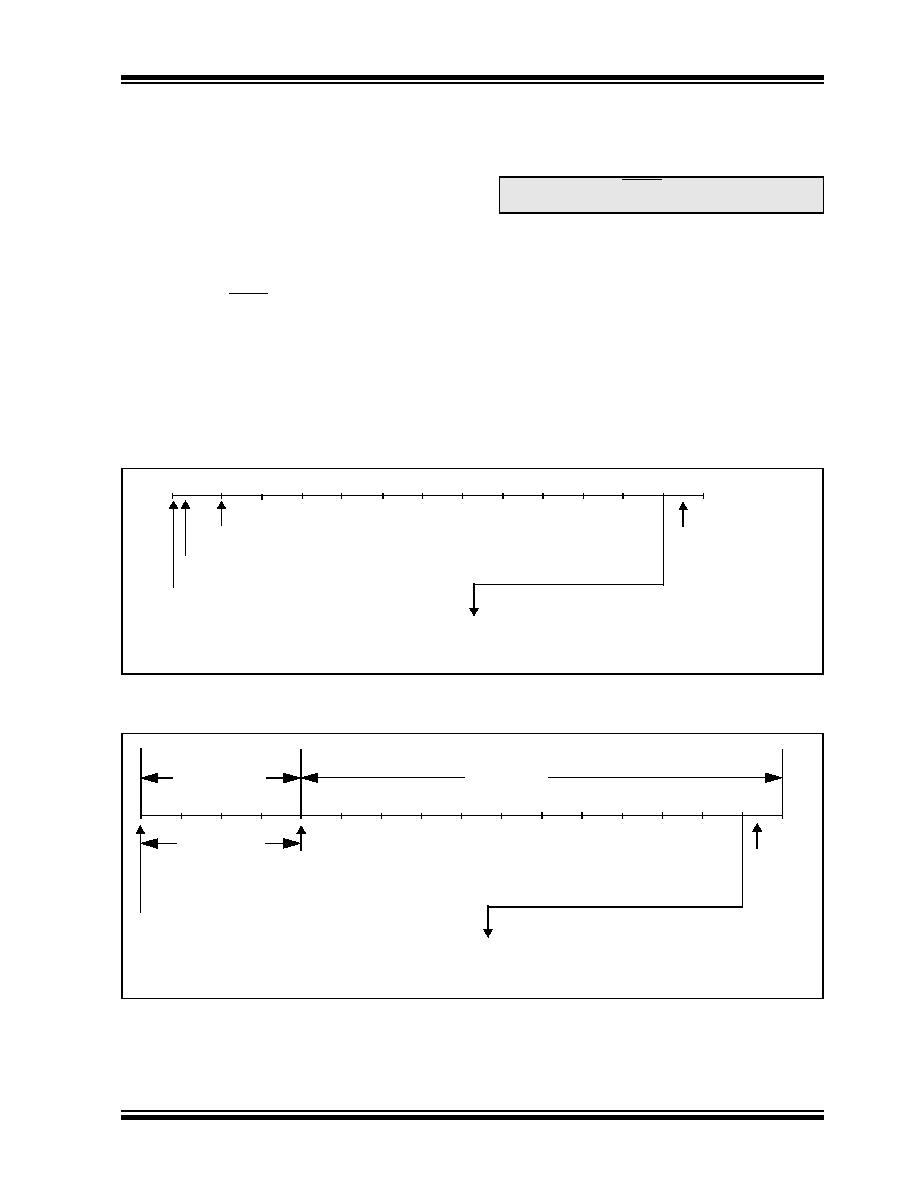

Figure 18-4 shows the operation of the A/D converter

after the GO bit has been set and the ACQT2:ACQT0

bits are cleared. A conversion is started after the follow-

ing instruction to allow entry into Sleep mode before the

conversion begins.

Figure 18-5 shows the operation of the A/D converter

after the GO bit has been set and the ACQT2:ACQT0

bits are set to ‘010’ and selecting a 4 TAD acquisition

time before the conversion starts.

Clearing the GO/DONE bit during a conversion will

abort the current conversion. The A/D Result register

pair will NOT be updated with the partially completed

A/D

conversion

sample.

This

means

the

ADRESH:ADRESL registers will continue to contain

the value of the last completed conversion (or the last

value written to the ADRESH:ADRESL registers).

After the A/D conversion is completed or aborted, a

2TAD wait is required before the next acquisition can be

started. After this wait, acquisition on the selected

channel is automatically started.

18.7

Discharge

The discharge phase is used to initialize the value of

the capacitor array. The array is discharged before

every sample. This feature helps to optimize the unity-

gain amplifier, as the circuit always needs to charge the

capacitor array, rather than charge/discharge based on

previous measure values.

FIGURE 18-4:

A/D CONVERSION TAD CYCLES (ACQT<2:0> = 000, TACQ = 0)

FIGURE 18-5:

A/D CONVERSION TAD CYCLES (ACQT<2:0> = 010, TACQ = 4 TAD)

Note:

The GO/DONE bit should NOT be set in

the same instruction that turns on the A/D.

TAD1 TAD2 TAD3 TAD4 TAD5 TAD6 TAD7 TAD8

TAD11

Set GO bit

Holding capacitor is disconnected from analog input (typically 100 ns)

TAD9 TAD10

TCY - TAD

ADRESH:ADRESL is loaded, GO bit is cleared,

ADIF bit is set, holding capacitor is connected to analog input.

Conversion starts

b0

b9

b6

b5

b4

b3

b2

b1

b8

b7

On the following cycle:

TAD1

Discharge

1

2

3

4

5

6

7

8

11

Set GO bit

(Holding capacitor is disconnected)

9

10

Conversion starts

1

2

3

4

(Holding capacitor continues

acquiring input)

TACQT Cycles

TAD Cycles

Automatic

Acquisition

Time

b0

b9

b6

b5

b4

b3

b2

b1

b8

b7

ADRESH:ADRESL is loaded, GO bit is cleared,

ADIF bit is set, holding capacitor is connected to analog input.

On the following cycle:

TAD1

Discharge

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

PIC18F86K22-I/PTRSL

MCU PIC 64K FLASH XLP 80TQFP

PIC16C63A-04I/SP

IC MCU OTP 4KX14 PWM 28DIP

PIC16C63A-04I/SO

IC MCU OTP 4KX14 PWM 28SOIC

52559-2270

CONN FFC 22POS .5MM VERT ZIF SMD

52559-1870

CONN FFC 18POS .5MM VERT ZIF SMD

DSPIC33EP64MC506-I/PT

IC DSC 16BIT 64KB FLASH 64TQFP

52745-1896

CONN FFC 18POS .5MM R/A ZIF SMD

PIC16LC622-04/P

IC MCU OTP 2KX14 COMP 18DIP

相关代理商/技术参数

PIC16F737-I/SP

制造商:Microchip Technology Inc 功能描述:IC 8BIT FLASH MCU 16F737 SDIL28

PIC16F737-I/SS

功能描述:8位微控制器 -MCU 7KB 368 RAM 25 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F737T-I/ML

功能描述:8位微控制器 -MCU 7KB 368 RAM 25 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F737T-I/SO

功能描述:8位微控制器 -MCU 7KB 368 RAM 25 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F737T-I/SS

功能描述:8位微控制器 -MCU 7KB 368 RAM 25 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F73-E/ML

功能描述:8位微控制器 -MCU 7 KB 368 RAM 25I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F73-E/SO

功能描述:8位微控制器 -MCU 7KB 192 RAM 22 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F73-E/SP

功能描述:8位微控制器 -MCU 7KB 192 RAM 22 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT